Altera Embedded Peripherals IP manuels

Manuels d'utilisation et guides de l'utilisateur pour Instruments de mesure Altera Embedded Peripherals IP.

Nous fournissons des manuels en pdf 1 Altera Embedded Peripherals IP à télécharger gratuitement par type de document : Manuel d'utilisateur

Altera Embedded Peripherals IP Manuel d'utilisateur (336 pages)

marque: Altera | Catégorie: Instruments de mesure | Taille: 3.10 MB |

Table des matières

Contents

2

Introduction

14

December

16

Timing Page

22

Min. Max

28

Interface

33

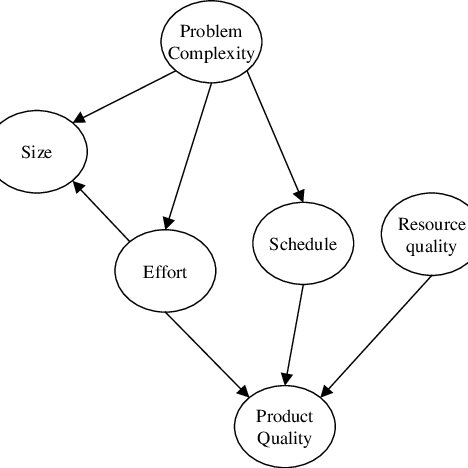

Architecture

38

UART Core

70

Flow Control

74

May 2008

86

16550 UART

87

DMA Support

91

Private APIs

99

Figure 9-7:

101

Driver Examples

102

UG-01085

103

2014.24.07

103

SPI Core

107

txdata

108

Receiver Logic

109

Configuration

111

Timing Settings

112

Software Files

114

Register Map

115

Date and

118

Document

118

Core Overview

119

PIO Core

123

Edge Capture

124

IRQ Generation

124

Input Options

126

Operation

132

PCI Lite Core

135

Avalon-MM Ports

137

Space Indicator

141

(Bits 1:0)

141

Description

141

Send Feedback

145

Simulation Flow

149

MDIO Core

151

Interfaces

153

Parameter

154

FIFO Settings

161

Software Control

163

Software Example

166

Parameters

177

Address Width

178

Feature Property

186

Transaction

190

DMA Descriptors

197

Error Conditions

198

Timeouts

206

Data Structure

207

SG-DMA API

208

Name Description

209

Overview

217

Component GUI

222

Byte Lanes

223

Length Field

224

Control Field

225

Status Register

229

Control Register

229

Advanced Options

235

Pixel Converter

246

Counter Size

251

Hardware Options

251

Mutex Core

258

Mutex API

260

Mailbox Core

264

Mailbox API

267

Register Maps

275

VIC IRQ RRS RIL

291

November

293

Altera FPGA

294

Core Behavior

295

System ID Core

298

Global Counter

302

Name (1) Meaning

305

PERF_BEGIN()

307

PERF_END()

308

PLL Cores

312

Registers

313

PLL Core

313

32-bit Counter

332

Software Access

334

IP Caveats

336

Plus de produits et de manuels pour Instruments de mesure Altera

| Modèles | Type de document |

|---|---|

| JESD204B IP |

Manuel d'utilisateur

Altera JESD204B IP User Manual,

158 pages

Altera JESD204B IP User Manual,

158 pages

|

| Low Latency Ethernet 10G MAC |

Manuel d'utilisateur

Altera Low Latency Ethernet 10G MAC User Manual,

109 pages

Altera Low Latency Ethernet 10G MAC User Manual,

109 pages

|

| LVDS SERDES Transmitter / Receiver |

Manuel d'utilisateur

Altera LVDS SERDES Transmitter / Receiver User Manual,

72 pages

Altera LVDS SERDES Transmitter / Receiver User Manual,

72 pages

|

| Nios II Embedded Evaluation Kit Cyclone III Editio |

Manuel d'utilisateur

Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual,

3 pages

Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual,

3 pages

|

| IP Compiler for PCI Express |

Manuel d'utilisateur

Altera IP Compiler for PCI Express User Manual,

372 pages

Altera IP Compiler for PCI Express User Manual,

372 pages

|

| Parallel Flash Loader IP |

Manuel d'utilisateur

Altera Parallel Flash Loader IP User Manual,

57 pages

Altera Parallel Flash Loader IP User Manual,

57 pages

|

| Nios II Embedded Evaluation Kit Cyclone III Editio |

Manuel d'utilisateur

Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual,

80 pages

Altera Nios II Embedded Evaluation Kit Cyclone III Edition User Manual,

80 pages

|

| Nios II C2H Compiler |

Manuel d'utilisateur

Altera Nios II C2H Compiler User Manual,

138 pages

Altera Nios II C2H Compiler User Manual,

138 pages

|

| RAM-Based Shift Register |

Manuel d'utilisateur

Altera RAM-Based Shift Register User Manual,

26 pages

Altera RAM-Based Shift Register User Manual,

26 pages

|

| RAM Initializer |

Manuel d'utilisateur

Altera RAM Initializer User Manual,

36 pages

Altera RAM Initializer User Manual,

36 pages

|

| Phase-Locked Loop Reconfiguration IP Core |

Manuel d'utilisateur

Altera Phase-Locked Loop Reconfiguration IP Core User Manual,

51 pages

Altera Phase-Locked Loop Reconfiguration IP Core User Manual,

51 pages

|

| SCFIFO |

Manuel d'utilisateur

Altera SCFIFO User Manual,

28 pages

Altera SCFIFO User Manual,

28 pages

|

| SDI II MegaCore |

Manuel d'utilisateur

Altera SDI II MegaCore User Manual,

89 pages

Altera SDI II MegaCore User Manual,

89 pages

|

| SerialLite II IP Core |

Manuel d'utilisateur

Altera SerialLite II IP Core User Manual,

110 pages

Altera SerialLite II IP Core User Manual,

110 pages

|

| Serial Digital Interface (SDI) MegaCore Function |

Manuel d'utilisateur

Altera Serial Digital Interface (SDI) MegaCore Function User Manual,

140 pages

Altera Serial Digital Interface (SDI) MegaCore Function User Manual,

140 pages

|

| 100G Development Kit, Stratix V GX Edition |

Manuel d'utilisateur

Altera 100G Development Kit, Stratix V GX Edition User Manual,

44 pages

Altera 100G Development Kit, Stratix V GX Edition User Manual,

44 pages

|

| 100G Interlaken MegaCore Function |

Manuel d'utilisateur

Altera 100G Interlaken MegaCore Function User Manual,

111 pages

Altera 100G Interlaken MegaCore Function User Manual,

111 pages

|

| Stratix V Avalon-MM Interface for PCIe Solutions |

Manuel d'utilisateur

Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual,

184 pages

Altera Stratix V Avalon-MM Interface for PCIe Solutions User Manual,

184 pages

|

| 10-Gbps Ethernet MAC MegaCore Function |

Manuel d'utilisateur

Altera 10-Gbps Ethernet MAC MegaCore Function User Manual,

175 pages

Altera 10-Gbps Ethernet MAC MegaCore Function User Manual,

175 pages

|

| Triple Speed Ethernet MegaCore Function |

Manuel d'utilisateur

Altera Triple Speed Ethernet MegaCore Function User Manual,

223 pages

Altera Triple Speed Ethernet MegaCore Function User Manual,

223 pages

|